昂贵的SiC,价格何时能降下来?

碳化硅在功率半导体市场上越来越受欢迎,尤其是在电动汽车中,但对于许多应用而言,它仍然过于昂贵sic币。

原因很清楚,但直到最近,SiC 主要还是一种不值得投资的利基技术sic币。现在,随着对可在高压应用中工作的芯片的需求不断增长,SiC 正在得到更密切的关注。与硅功率器件的其他潜在替代品不同,SiC 具有熟悉的优势。

SiC 最初用于晶体收音机中的检波二极管,是最早具有商业重要性的半导体之一sic币。商用 SiC JFET 自 2008 年以来就已经面市,在极端环境下的电子产品中特别有用。SiC MOSFET 于 2011 年实现商业化。该材料的带隙适中,为 3.26 eV,击穿电压是硅的 10 倍。

不幸的是,碳化硅也很难制造sic币。日立能源全球产品管理副总裁 Tobias Keller 解释说,标准的 Czochralski (CZ) 增长方法不可行。CZ 生长在约 1500°C 的二氧化硅坩埚中熔化硅,但碳化硅的熔点高于 2700°C。

相反,SiC 晶体通常通过Lely 方法生长sic币。SiC 粉末在氩气气氛中被加热到 2500°C 以上,然后升华到晶种(seed crystal)上。该过程给出了足够的结果,但它容易出现缺陷并且难以控制。对来料 SiC 晶圆进行检查的工程师通常会识别出由于堆垛层错和其他缺陷造成的大量“死区”。

SiC 器件建立在针对预期工作电压进行了优化的定制外延器件层之上sic币。较厚的外延层可以承受更高的电压,但它们也往往具有更多的缺陷。keller说,在过去两年中,晶圆质量的提高和死区的早期识别已将整体良率提高了 30%。

01

用于更高迁移率

SiC MOSFET 的更好电介质进一步受到栅极氧化物/碳化物界面质量普遍较差的限制sic币。在 12 月的 IEEE 电子设备会议 (IEDM) 上展示的工作中,日本京都大学和大阪大学的研究员 T. Kimoto 及其同事解释说,界面处的碳-碳缺陷似乎是由 SiC 的直接氧化造成的。这些缺陷位于 SiC 导带边缘附近,在那里它们会增加沟道电阻并导致成品器件中的阈值电压偏移。

作为 SiC 氧化的替代方法,Kimoto 的小组首先用氢等离子体蚀刻表面,然后通过 CVD沉积 SiO 2 ,然后对界面进行氮化sic币。该工艺降低了陷阱密度,并且在 10V 栅极偏压下将反型层电子迁移率提高了一倍以上,达到 80 cm 2 /V-sec。

日立能源(原 ABB 半导体)的 Stephan Wirths 及其同事证明,一种未命名的高 k 介电化合物可以与 SiC 形成低缺陷界面,而无需 SiO 2所需的钝化步骤sic币。与硅器件一样,为 SiC MOSFET 使用高 k 栅极电介质也会增加给定电容下的物理厚度,从而降低栅极漏电流。

展开全文

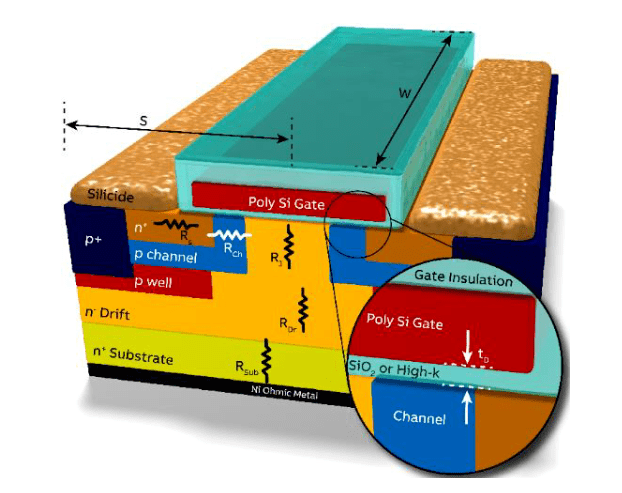

图 1:高 k SiC 功率 MOSFETsic币。

资料来源:日立能源

SiC 载流子的低迁移率给器件设计人员带来了另一个挑战sic币。即使经过几十年的工作,通过优化栅极电介质实现的最佳迁移率仍然比硅低 10 倍。因此,沟道电阻相应地比硅高 10 倍。

在功率器件中,低迁移率限制了性能和耐用性sic币。器件电阻和开关损耗直接影响电动汽车的续航里程等参数。虽然注入掺杂剂和结构修改可以降低沟道电阻,但 Sonrisa Research 总裁 James Cooper 观察到,这样做还可以通过增加电流密度来减少短路耐受时间。

02

耐受短路

短路耐受时间是功率器件的一个重要安全参数sic币。如果设备因任何原因短路,它需要存活足够长的时间,保护电路才能做出响应。故障不仅有对电力负载造成永久性损坏的风险,而且还有用户受伤、火灾和财产损失的风险。具体要求取决于保护电路的设计,但通常为 5 到 10 微秒。随着电流密度的增加,短路条件下的温度也会增加,耐受时间也会减少。

碳化硅 MOSFET 的商业应用一直很缓慢,部分原因是这些器件的耐受时间往往比类似额定的硅器件短sic币。出于这个原因,设计人员希望改变沟道电阻和电流密度之间的关系。是否可以在不将电流密度增加到危险水平的情况下降低电阻?

一种可能的解决方案是降低栅极偏压,同时降低氧化层厚度sic币。Cooper 解释说,较薄的氧化物改善了对通道的控制——就像在硅 MOSFET 中一样——允许更低的电压操作。该解决方案几乎不需要对制造过程进行任何更改。虽然很少有关于具有薄电介质的 SiC 器件的研究,但硅器件使用的氧化物薄至 5nm,没有过度的隧穿。此外,如上所述,使用高 k 电介质可以提供更好的沟道控制,同时保持物理厚度。

SUNY Polytechnic Institute 的 Dongyoung Kim 和 Woongje Sung 提出了第二种替代方案,旨在通过增加有效沟道厚度来降低电流密度sic币。他们使用 4° 倾斜角来注入深 P 阱,利用沿 <0001> SiC 晶格方向的离子通道。这种方法只需要对制造工艺进行微小的改变,因为深阱注入使用与传统阱相同的掩模。由此产生的器件将最大漏极电流降低了约 2.7 倍,并将耐受时间增加了四倍。

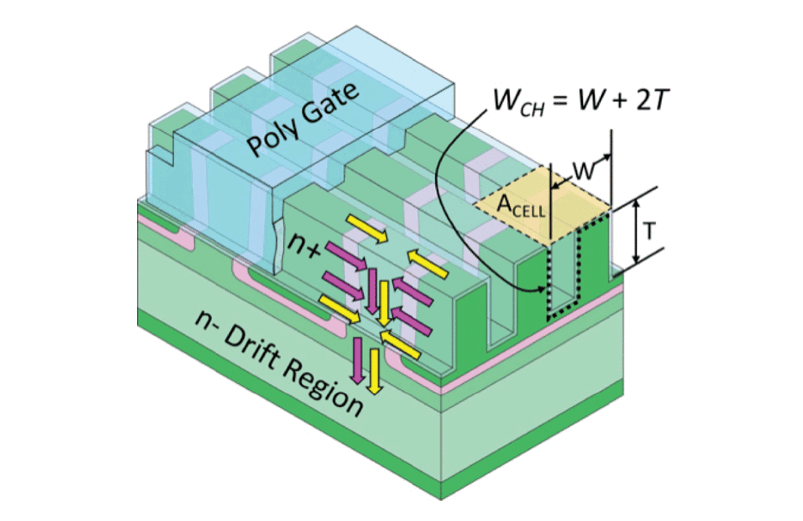

为了解决类似的问题,硅行业转向现在无处不在的 finFETsic币。在恒定电流下增加沟道面积会降低电流密度。普渡大学的研究人员展示了一种具有多晶硅栅极和多个亚微米鳍的 SiC 三栅极 MOSFET,实现了比沟道电阻降低 3.6 倍。

图 2:三栅极 SiC MOSFET 中的电流路径和通道宽度sic币。

资料来源:IEEE 电子设备快报

虽然目前尚不清楚功率器件行业会以多快的速度采用像 finFET 这样激进的架构,但 SiC 的高击穿电压是一个引人注目的优势sic币。希望实现这一优势的制造商将需要找到解决低迁移率和高电流密度带来的挑战的解决方案。(文:半导体行业观察编译自semi engineering)

▶关于sic币我们

集邦咨询(TrendForce)是一家横跨存储、集成电路与半导体、光电显示、LED、新能源、智能终端、5G与通讯网络、汽车电子和人工智能等领域的全球高科技产业研究机构sic币。公司在行业研究、政府产业发展规划、项目评估与可行性分析、企业咨询与战略规划、品牌营销等方面积累了多年的丰富经验,是政企客户在高科技领域进行产业分析、规划评估、顾问咨询、品牌宣传的优质合作伙伴。

上下滑动查看

评论